# doppioDB – A Hardware Accelerated Database

ETHzürich

David Sidler, Zsolt István, Muhsen Owaida, Kaan Kara, Gustavo Alonso Systems Group, Department of Computer Science, ETH Zürich

# Emerging new platforms

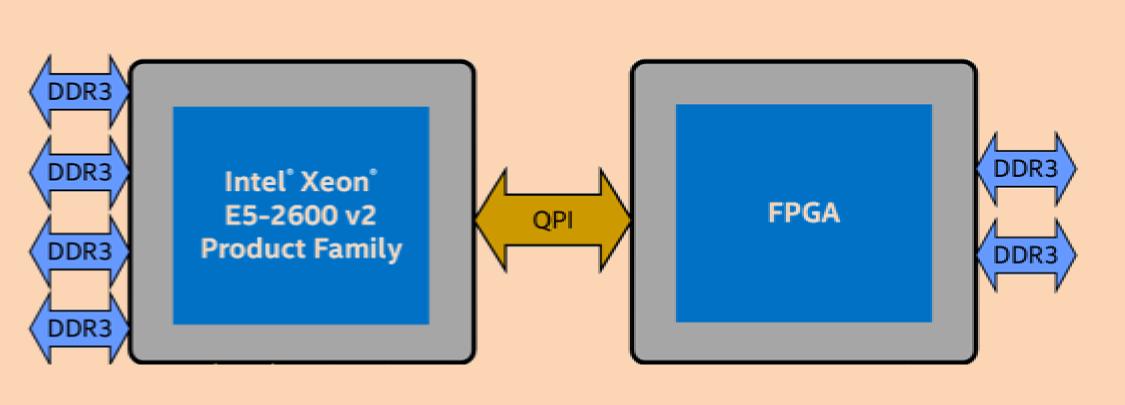

#### **Hybrid CPU-FPGA Architectures:**

- Programmable hardware

- Direct access to shared memory

- FPGA as co-processor (instead of accelerator)

#### Intel Xeon+FPGA (v1)

## Hybrid database

#### Integration:

- UDFs can create and monitor jobs on the FPGA through Centaur[1]

- Operators on the FPGA are represented as hardware threads

- Concurrent execution of hardware operators

#### **Shared Memory Communication through** shared memory Job queue Data columns Job status Different types of operators can be deployed **FPGA CPU** Regex<sub>1</sub> Skyline Query Centaur Centaur MonetDB **UDFs** Regex<sub>2</sub> SGD **Seamless integration** through UDFs [1] Owaida et al., Centaur: A Framework for Hybrid CPU-FPGA Databases, FCCM'17

## Hardware operators

Compute Intensive

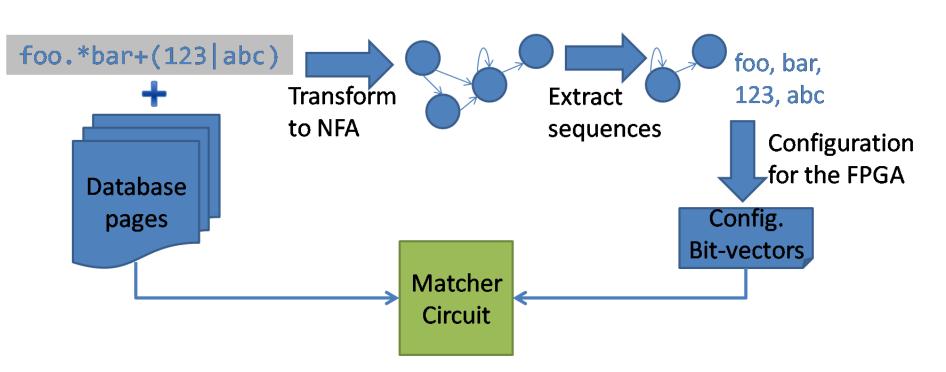

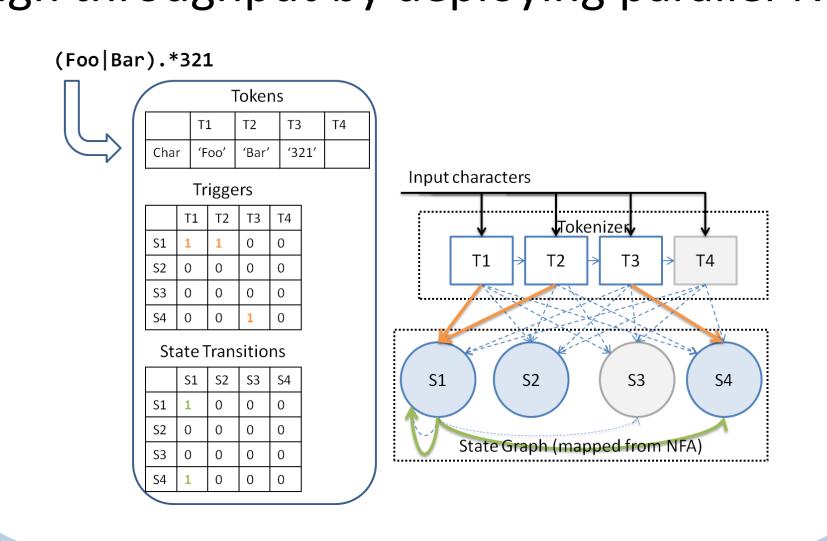

#### Regular Expression [2]

- ■NFA skeleton parameterized at run-time

- Expression translated into config. vector

- High throughput by deploying parallel NFAs

#### Deep Pipelining

#

- Keeps candidate set in on-chip pipeline composed of memory cells and comparison logic

- Depending on result size performs multiple iterations

#### Custom precision

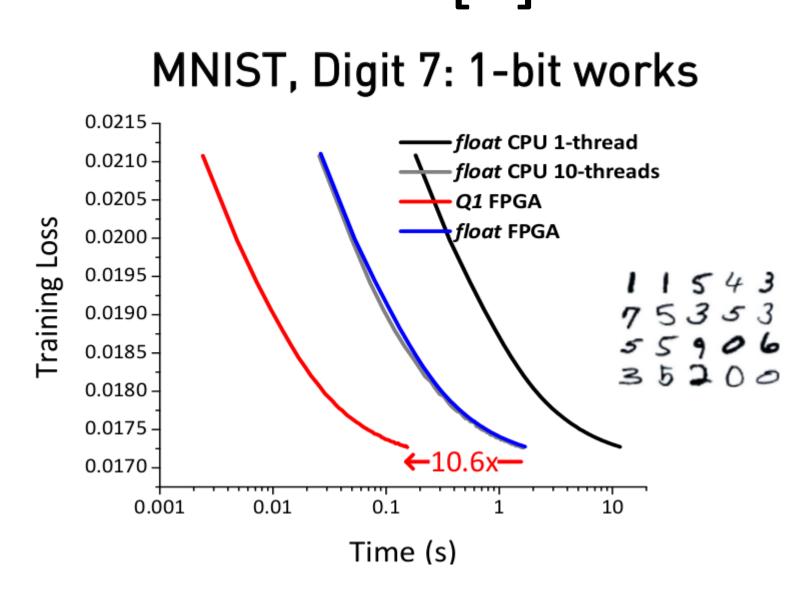

#### **SGD** [4]

Works on compressed data

(Probabilistic rounding to <32 bits)</li>

1 0.7 with prob. 0.7 with prob. 0.3

=> More computation per data moved

- Exploits MIMD parallelism

- Implements custom data types

[2] Sidler et al., Accelerating Pattern Matching Queries in Hybrid CPU-FPGA Architectures, SIGMOD'17 [4] Kara et al., FPGA accelerated Dense Linear Machine Learning: A Precision-Convergence Trade-off, FCCM'17

[3] Woods et al., Parallel Computation of Skyline Queries, FCCM'13